## **DVT IDE**

For SystemVerilog, Verilog, Verilog-AMS, VHDL, PSL, e\*, PSS\*, UPF\*, and CPF\*

The complete development environment for hardware design and verification

Available for both Visual Studio (VS) Code and Eclipse platforms

#### 10 REASONS TO CHOOSE DVT IDE

- See the errors flagged by incremental compilation as you type

- Write code faster using autocomplete and error fix suggestions

- Quickly move around in the source code using hyperlinks

- Query the project database to accurately locate relevant information

- Easily create and reuse code and project templates

- Continuously improve your source code using refactoring operations

- Easily understand the project structure using high-level views

- 8 Visualize the project architecture using UML and HDL diagrams

- Trace signals throughout the design

- 10 Place reminders and track tasks

### BENEFITS

Increases productivity and reduces time to market

Speeds up source code development

Enables efficient reading and understanding of complex source code

Simplifies debugging and legacy source code maintenance

Ensures higher quality source code development

Streamlines code review

Accelerates language and methodology learning

#### OVERVIEW

Design and Verification Tools (DVT) IDE is an integrated development environment for SystemVerilog, Verilog, Verilog-AMS,VHDL, PSL, the e language\*, PSS\*, UPF\*, and CPF\*. It is similar to well-known programming tools such as Visual Studio®, NetBeans®, and Intellij®.

DVT IDE consists of a compiler, a smart code editor, an intuitive graphical user interface, and a comprehensive set of features that help with code writing, inspection, navigation, and debugging. It provides capabilities that are specific to the hardware design and verification domain, such as design diagrams, signal tracing, power domain visualization, and verification methodology support.

DVT IDE is a powerful tool that allows your engineers to overcome the limitations of plain text code editors and address today's project complexity more efficiently. It enables faster and smarter code development and simplifies legacy code maintenance for novices and experts alike.

#### **IEEE Standard Compliant Compiler**

The compiler is compliant with the IEEE 1800™ SystemVerilog, IEEE 1076™ VHDL, IEEE 1850™ PSL, IEEE 1647™ e Language\*, and IEEE 1801 ™ Low Power\* standards. Besides fully supporting the design and verification languages, DVT IDE also flags the use of non-standard compliant language constructs, which ultimately increases cross-simulator compatibility.

#### Integration with Simulators and Other Tools

DVT IDE integrates with all major hardware simulators to simplify simulation analysis. It also works with revision control systems such as Git, Subversion, and ClearCase, and bug tracking systems such as Jira™ and Bugzilla.

#### **Platform Ready**

DVT IDE for VS Code is built on the widely adopted Visual Studio Code platforms. DVT Eclipse IDE is built on the powerful Eclipse Platform used by millions of engineers worldwide. Both versions inherit the best features and practices collected into its base platform. DVT IDE integrates within a large plug-in ecosystem and works flawlessly with third-party extensions.

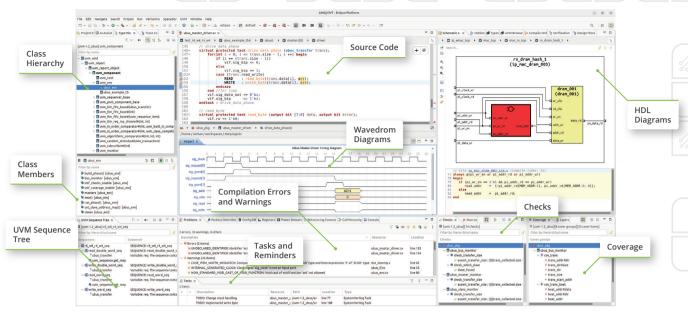

DVT Eclipse IDE Overview

### EFFICIENT CODE WRITING AND SIMPLIFIED MAINTENANCE

#### **Advanced Code Editing Features**

DVT IDE incorporates advanced code editing features such as:

- On-the-fly syntactic and semantic checking

- Error fix suggestions

- Autocomplete and autoinstance

- Source code refactoring operations

- In-line reminders and task tracking\*

- Customizable code and project templates

- Macro expansion

- Dedicated wizards to generate getters and setters or override functions

- Highly configurable source code formatting

- Integration with revision control systems

- Vi and Emacs emulation

DVT IDE performs on-the-fly incremental compilation. There is no need to invoke the simulator to make sure the code compiles with no errors. DVT IDE's smart editor highlights the errors in real time, as you type. As a result, users can make the necessary corrections on the spot. To assist with error correction, DVT IDE also provides fix proposals such as "did you mean" when detecting a potential typo and "update instance" when module ports have changed. Moreover, the developer or reviewer can quickly locate and fix various issues spread throughout the code using the Problems View where all errors and warnings are listed.

Autocomplete provides a context-sensitive list of proposals for partially entered text. This capability helps avoid typos and eliminates the need to search for definitions in other files. Autoinstance allows engineers to quickly instantiate and connect a module or entity when needed.

Refactoring allows users to perform semantic changes in code. While a plain text editor or grep/sed utility is limited to simple search and replace actions, DVT IDE can accurately perform powerful operations like "rename method foo() of class bar" and "rename signal x of module y."

All the definitions and places where the method or signal is used are precisely updated. Users can also "extract this piece of code into a separate function and "add a new port p

to module m." Refactoring helps engineers avoid tedious and error-prone operations such as scrolling through long lists of irrelevant plain text matches or repetitive copy and paste.

In DVT Eclipse IDE, in-line reminders, such as TODO, FIXME, and customized tags can be placed in code comments. These reminders are listed in the Tasks View. With a simple click, users can jump directly to the source code lines of the selected task. In-line reminders are also useful when performing code review. Since the action items are inside the source code, they are always up to date and visible to the whole team. The task list can also be used to estimate the code status and remaining development effort. Similar functionality is available in DVT IDE for VS Code by use of a third-party plugin.

Code templates are parameterized code snippets. Combined with TODO tags, this capability enables your users to easily follow the project development guidelines. Project templates generalize code templates and allow engineers to start a new project from a reference project layout.

Errors inside macros are difficult to investigate. With DVT IDE's macro expansion feature, engineers can examine and debug macro code fragments in context with the source code.

#### **Code and Project Navigation Features**

Maintaining tens of thousands of lines of code can be challenging. DVT IDE simplifies maintenance by providing capabilities such as:

- Hyperlinks

- Breadcrumb navigation bar

- Project database queries

- Semantic search for usage, writers, or readers

- Structural views

- Signal tracing

- UML and HDL diagrams

- Comments and macro or parameter values in tooltips

- Semantic source code coloring

These features enable users to navigate easily through complex code, locate the relevant information faster, and understand the source code quickly. They also reduce project costs, by allowing users to avoid locking a simulator license just to inspect the design hierarchy or the verification environment architecture.

DVT IDE for VS Code

Hyperlinks help navigate faster through multiple project files. This practically eliminates the need for using the grep command or memorizing details such as file names and locations. To look up the definition of an element, users can simply hover the mouse over the element name to turn it into a hyperlink. This saves time by jumping directly to the element definition instead of having to search for it.

The editor and diagrams show a breadcrumb navigation bar that clearly indicates the current location in the design hierarchy. It enables engineers to quickly find their way and easily move up and down in the design as needed.

Project database queries allow users to quickly locate specific elements. For example, typing a few letters in a search bar locates a specific module, entity, class, macro, assertion, or coverage item.

Semantic search for usage lets users quickly find out who is calling "method foo," who is using "signal clk of module fifo," or "what are all the constraints on packet size." It is also very easy to quickly locate all places where a variable, signal or parameter is written or read, as well as where events are emitted.

Unlike plain text grep/sed searches, the semantic search results are accurate. For example, a search for "who is calling method foo of class a" will not match calls to "method foo of some other class b."

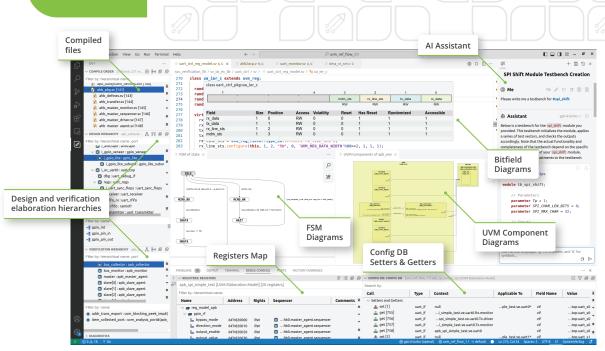

To help in understanding the project architecture, DVT IDE offers structural views for examining design and verification elaboration hierarchies, class type hierarchies, and function call hierarchies.

Using the signal tracing functionality, designers can effortlessly locate the signal source, an operation called "show writers," or the signal destination, an operation called "show readers." The signal trace can also be visualized as a diagram.

DVT IDE enables your engineers to inspect a project through diagrams. Designers can use HDL diagrams such as schematic, state machine, and flow diagrams. Verification engineers can use UML diagrams such as inheritance and collaboration diagrams. Bit field diagrams for packed data structures and UVM registers are also automatically generated. Diagrams are hyperlinked and synchronized with the source code and can be saved for documentation purposes. Users can easily search and filter diagrams as needed, for example, visualizing only the clock and reset signals in a schematic diagram.

Semantic source code coloring simplifies reading. For example, inactive pre-processing regions are grayed-out, input ports are visibly distinct from output ports, and local variables and class variables have different colors.

In the design or verification source code, users can include waveform specifications using the popular open-source WaveDrom format. These specifications are automatically rendered as waveforms.

#### PREPROCESSED FILES SUPPORT

DVT IDE provides full IDE capabilities when working with files that contain "preprocessor" statements in other languages such as Perl and Python's Jinja2 library, or in proprietary languages. Even if the actual code for simulation is generated in subsequent steps from such files, all the features like navigational hyperlinks, autocomplete, on-the-fly error detection, quick fixes, refactoring, etc. work smoothly as if using files written using only a single language.

### VERIFICATION METHODOLOGY SUPPORT

DVT IDE supports the Universal Verification Methodology (UVM). Its powerful UVM-oriented features help users learn UVM faster, accelerate adoption, and build UVM verification environments with ease.

DVT IDE executes the UVM runtime elaboration phase allowing users to view their testbench structures accurately reflecting the configuration at the start of simulation. Users can debug the UVM elaboration phase by easily adding breakpoints, stepping through the source code, and inspecting variable values and call stacks.

Users can easily browse through UVM-based classes such as agents, monitors, and sequences, examine component trees, visualize architecture diagrams including TLM port connections, browse register maps, search for factory related constructs or config db getters and setters that may influence the testbench behavior, and generate code using UVM specific code templates and wizards.

DVT IDE users can interactively run the Verissimo System-Verilog Linter product, including its checks for SystemVerilog and UVM compliance. Verissimo provides hundreds of customizable rules and advanced capabilities for a thorough audit of testbenches.

#### **LOW POWER SUPPORT\***

DVT IDE reads UPF or CPF power format files and presents power domains in diagrams, design hierarchies, tooltips, and the breadcrumb navigation bars. Any changes to UPF or CPF files are incrementally analyzed, and power domains updated on the fly. Such capabilities simplify power domain design and debugging.

## SIMULATOR AND CODE ANALYSIS INTEGRATION

Users can start a simulation, run synthesis, or invoke any code analysis tool directly from DVT IDE and browse its output. Customizable problem matchers grep the standard output in order to detect error or warning messages and connect them with the source code. All errors and warnings are presented in the Problems View, allowing users to quickly jump to the source of the error or warning. By providing such log recognition, DVT IDE significantly simplifies and speeds up analysis and debugging.

### CROSS-LANGUAGE CAPABILITIES FOR MIXED-LANGUAGE PROJECTS

The cross-language capabilities allow users to work with source code written in multiple languages and easily understand the whole design. Features such as hyperlinks, design hierarchy browsing, HDL diagrams, and signal tracing work across SystemVerilog/Verilog, VHDL, and C/C++ sources\*. For example, a user can click on an instance in Verilog and jump to its VHDL definition. A user can also click on a SystemVerilog DPI call and jump to its C definition.\*

#### PORTABLE STIMULUS SUPPORT\*

The Portable Stimulus Standard (PSS) allows the creation of higher-level verification tests that are portable from IP to system and from simulation to hardware. A large number of test scenarios can be generated from a single PSS description. DVT IDE provides support for creating and editing PSS code, solves the behavior expressed in the model, and displays examples of valid scenarios. Visualization of detailed scenarios makes it easier for users to determine whether the abstract PSS model is correct.

#### AI ASSISTANT

Al Assistant allows engineers to use large language models (LLMs) to generate new code or explain and improve the existing code base. They can compose requests including information from the DVT IDE compilation database to improve the accuracy of LLM responses. Furthermore, DVT IDE incrementally

compiles the newly generated code and Verissimo SystemVerilog Linter incrementally checks it for coding guideline violations. Such capabilities significantly increase code development efficiency.

Al Assistant supports a wide range of popular LLMs from OpenAl, Github Copilot, Google Al, Anthropic, and locally hosted Ollama. In addition to supporting both commercial, open weight, and open source models, DVT IDE can easily connect to in-house proprietary LLMs. To ensure confidentiality when working with third-party LLMs, users can preview all communication with the LLM and make sure that no proprietary IP is being transferred.

# INCREASING DESIGN AND VERIFICATION PRODUCTIVITY AND QUALITY

#### **Faster and Smarter Code Development**

DVT IDE was developed with maximizing the design and verification productivity in mind. Users do not need to switch from the editor to the simulator, browser, or console and therefore they can focus on code writing and review. Moreover, DVT IDE substantially reduces the time spent performing repetitive tasks such as locating a class or module definition, finding all places where a function is called, renaming a variable, and searching for relevant information in large source code files or documentation.

By using hyperlinks, autocomplete, in-line documentation, semantic search, and smart log view features users can find what they need through a single click or shortcut. As a result, the speed and quality of code development increase significantly.

#### **Efficient Project Management**

DVT IDE helps manage your design and verification projects more efficiently. The ability to easily review the source code using features such as hyperlinks, project database queries, structural views, and HDL or UML diagrams enables both managers and engineers to see the whole picture clearly and control a project from a higher perspective. Action item tracking using in-line reminders listed in the Tasks View allows the team lead or manager to better organize and control the development effort.\*

#### Lower Language Learning Curve

Beginners feel comfortable with the DVT IDE friendly user interface. In addition, the combination of features such as compilation errors highlighted as you type, error fix proposals, autocomplete, and code templates together with the access to integrated documentation speed up the learning process.

#### INTEGRATED SOLUTION

**DVT IDE** is closely integrated with the other design and verification products available from AMIQ EDA, including **Verissimo SystemVerilog Linter**, **Specador Documentation Generator**, **and DVT Debugger\***.

#### **TECHNICAL SUPPORT**

The technical support team is available to promptly answer your questions, provide you with training, and work with you to determine your needs. Your requirements and feedback are important. Whether you are looking for technical support or new features to improve your design and verification flow, AMIQ's technical support team strives to answer your requests in a timely manner.

\*Feature is currently available in DVT Eclipse IDE only

#### CONTACT AMIQ

SUPPORT & EVALUATION support@amiq.com

SALES sales@amiq.com

Copyright 2025 AMIQ EDA S.R.L.

All rights reserved.

The information contained herein is

The information contained herein is subject to change without notice.

BSITES