Diagrams

Specador has the ability to automatically generate diagrams after the compilation is done.

Tip

Diagrams can be zoomed, panned or opened in full screen for better inspection. Click on a class or block to jump to the chapter where it is documented.

Type |

Diagram |

Observations |

|---|---|---|

Block Diagram |

Presents all the ports and parameters, highlighting busses and clocks

|

|

Flow Diagram |

Presents a high level view of internal connectivity. Multiple connections from one instance to another are collapsed in a single directional edge

|

|

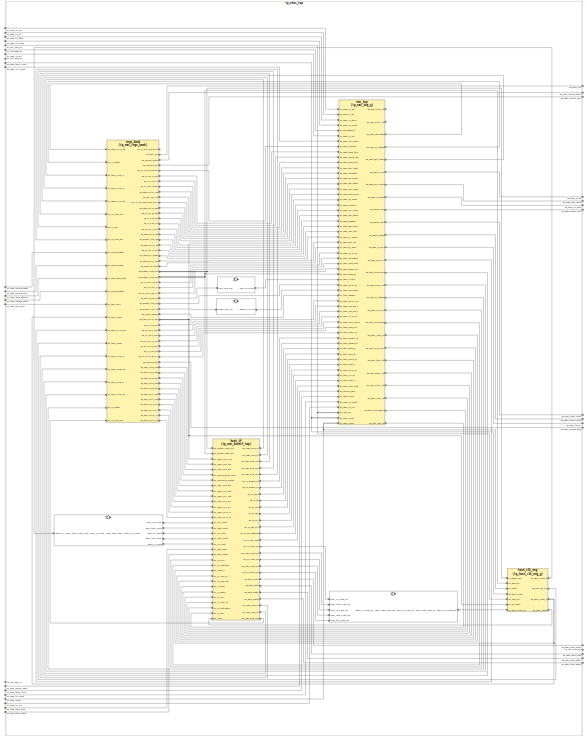

Schematic Diagram |

|

Presents the internal structure (ports, sub-instances, combinational and sequential logic and connections)

|

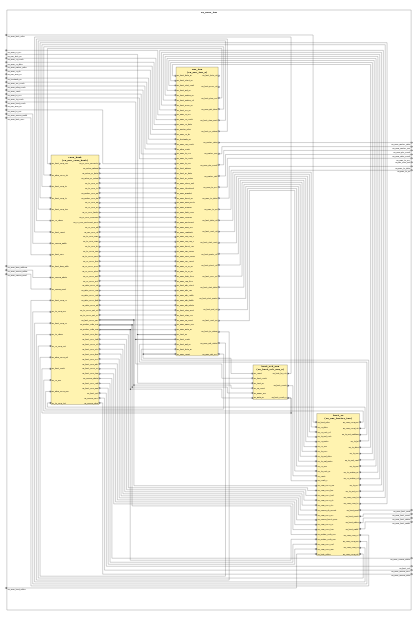

Sub-Instances Diagram |

|

Presents the internal structure without combinational and sequential logic

|

Finite State Machine Diagram |

Presents states and transitions by analyzing all the assignments and conditions in which a state variable is used

|

|

WaveDrom Diagram |

WaveDrom is a tool that draws timing diagrams (waveforms) from a simple textual description written in JSON.

To export such diagrams, they must be enclosed between

@WAVEDROM_START and @WAVEDROM_END pragmas inside comments.Note Specador uses WaveDrom 3.5.0. |

|

Bit Field Diagram |

Available for packed data types and UVM registers. Note Diagrams are rendered using the BitField library. |

|

UML Inheritance Diagram |

Presents the inheritance hierarchy including the derived classes and the members of the class |

|

UML Collaboration Diagram |

Presents all associations with other classes |

|

UVM Components Diagram |

UVM Components Diagrams help you inspect and document the structure of a verification environment

|

|

External Generated Diagram |

In order to generate diagrams using external scripts, the description needs to be enclosed between Available options when writing custom diagram descriptions:

Important Specador will invoke the generator as follows: @program @input_file @output_file @args SystemVerilog module parameters and macros default values can also be passed to the input description using the following syntax:

|