Descriptor Lists and Data Buffers

The EMAC transfers frame data to and from receive and transmit buffers in host memory. The descriptors resides also in the host memory and acts as pointers to these buffers.

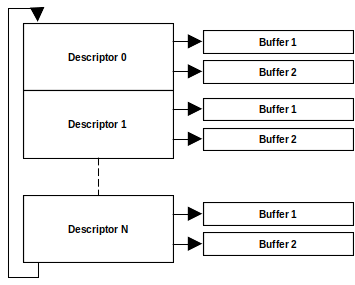

There are two descriptor lists, one for the receive buffers and one for transmit. The base address of each list is written into CSR3 and CSR4, respectively. A descriptor list is forward-linked, either implicitly or explicitly. The last descriptor may point back to the first entry to create a ring structure. Explicit chaining of descriptors is accomplished by setting the second address chained in both receive and transmit descriptors. The descriptor lists reside in the host physical memory address space. Each descriptor can point to a maximum of two buffers. This enables two buffers to be used, physically addressed, and not contiguous in memory.

A data buffer consists of either an entire frame or part of a frame, but it cannot exceed a single frame. Buffers contain only data. The buffer status is maintained in the descriptor. Data chaining refers to frames that span multiple data buffers. Data chaining can be enabled or disabled. The data buffers also reside in the host physical memory space.

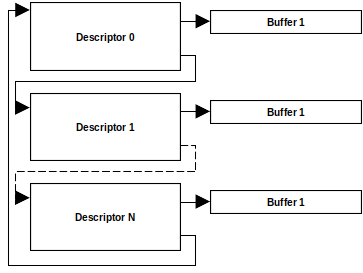

Descriptor Ring Configuration:

Descriptor Chain Configuration: