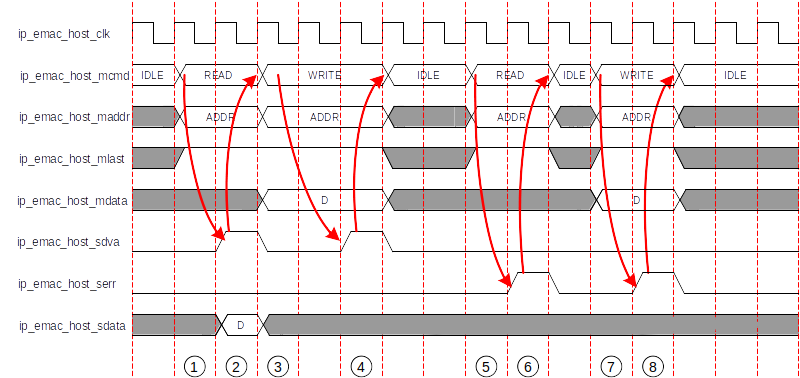

Host Master Interface Single Read/Write Timing

This figure presents the host interface timing when single commands are used. The ip_emac_host_mlast asserted high indicates that single command is issued. The ip_emac_host_mcmd transition to IDLE is determined by the assertion of ip_emac_host_sdva or ip_emac_host_serr signal. After the slave response for the current command the next command is loaded by the ip_emac_host_mcmd if available, else the IDLE state is loaded.

The EMAC issues a single READ command

The slave responds by asserting ip_emac_host_sdva and ip_emac_host_sdata

The EMAC issues a single WRITE command

The slave accepts the WRITE command by asserting ip_emac_host_sdva

The EMAC issues a single READ command

The slave responds by asserting ip_emac_host_serr (the transfer cannot be complete by the slave)

The EMAC issues a single WRITE command

The slave responds by asserting ip_emac_host_serr (the transfer cannot be complete by the slave)