In a world dominated by proprietary architectures such as x86 and ARM, RISC-V stands out with its open and flexible approach, redefining how processors are designed and used. As an open-source instruction set architecture (ISA), RISC-V allows developers to customize and optimize hardware solutions without the constraints of commercial licensing.

But what does this mean in practice? In this article, we will explore what RISC-V is, how it works, and its advantages and disadvantages. Whether you are a developer, hardware engineer, or simply passionate about innovation, this guide will provide you with a clear understanding of RISC-V’s potential and its impact on the semiconductor industry.

What Is RISC-V?

RISC-V is an open-source ISA used for processor development. Based on the principles of reduced instruction set computing (RISC), it provides a simple, clean design that enables efficient processor performance while fostering innovation through its open and modular architecture. RISC-V is designed to be freely available for academic, research, and commercial use without proprietary restrictions.

History

RISC-V originated from research efforts at the University of California, Berkeley, around 2010 and has since evolved into a globally-recognized ISA that emphasizes simplicity, modularity, and extensibility. Unlike many other processor architectures that are controlled by large corporations, RISC-V was created as an open standard, which has significantly influenced its adoption in both academia and industry.

RISC-V’s development reflects a broader movement within the semiconductor industry towards open-source hardware. Its open nature allows designers to modify and extend the architecture to meet specific needs, ranging from low-power embedded systems to powerful data centers. Over time, the community-driven approach has led to the proliferation of multiple RISC-V implementations—from simple microcontrollers to advanced cores designed for high-performance applications.

The evolution of RISC-V is marked by milestones such as the release of the original ISA specifications, the formation of the RISC-V Foundation (now RISC-V International), and the widespread adoption by numerous companies and research institutions. This openness has stimulated innovation, enabling smaller organizations and academic institutions to contribute to and benefit from a rich set of design and verification resources.

How Does RISC-V Work?

The RISC-V architecture operates on a simplified set of instructions, which streamlines the processor design and allows for higher performance and energy efficiency. The RISC-V ISA is organized into a base integer instruction set, denoted as RV32I or RV64I for 32- and 64-bit implementations, respectively. This base is supplemented by various optional standard extensions, such as the M (multiply/divide), A (atomic operations), F (floating-point), and D (double-precision floating-point) extensions.

The core principle behind RISC-V is its clean-slate design approach with the following key characteristics:

- Modular structure: RISC-V is built so that only the necessary features are implemented, with the option to include additional functionalities as extensions. This modularity means implementations can be tailored to specific applications without the complexity inherent to monolithic implementations.

- Simplicity: ISA implementations focus on simplicity, reducing the number of instructions and addressing modes. This simplicity makes the hardware easier to design, verify, and optimize, resulting in improved performance while lowering the complexity of the compiler and toolchain.

- Scalability: The RISC-V processor architecture supports a wide range of systems, from microcontrollers in Internet-of-things (IoT) devices to high-performance computing platforms. This scalability is largely due to the clear definition of core instruction sets and optional extensions, facilitating both low-power embedded designs and high-end processors.

- Open and extensible: Since RISC-V is not burdened by licensing fees, companies and researchers are free to innovate and even create custom extensions beyond the standard offering. This freedom drives a diverse ecosystem and encourages experimentation and tailored design practices.

Internally, a RISC-V processor follows a typical RISC pipeline architecture. Instructions are fetched, decoded, executed, and then written back in a streamlined process that reduces overhead and minimizes the number of clock cycles per instruction (CPI). The design also supports out-of-order execution and advanced branching techniques in more complex implementations. Moreover, memory management is handled through standard mechanisms including paging and virtual memory, with future plans including security enhancements such as trusted execution environments and encrypted computation.

Overall, RISC-V’s operational model is built around the idea of “less is more,” where a lean instruction set can lead to simple and efficient hardware designs that remain highly flexible and extensible.

Benefits

RISC-V is transforming the semiconductor industry with its innovative architecture, established as a solid alternative to proprietary processor architectures. This ISA is popular among developers due to its wide range of benefits:

- Open-source nature: The lack of licensing fees, combined with the flexibility to customize the ISA, gives developers greater control and drives cost-efficient innovation.

- Modular design: RISC-V allows system architects to build processors tailored to specific application needs—whether for ultra-low-power sensors or high-performance computing units—without incurring the overhead of irrelevant features.

- Simplicity: RISC-V facilitates a shorter design cycle. With fewer instructions and a straightforward structure, developers can more easily verify and validate designs, thereby reducing time-to-market.

- Security: RISC-V offers robust security features through open-source reference designs, software composition analysis tools, and security extensions. Its transparent, open-source architecture allows for thorough public scrutiny, ensuring that vulnerabilities, backdoors, and hidden channels can be identified and eliminated.

- Ecosystem: The active community and the numerous available IP implementations, tools, simulators, and educational resources have accelerated adoption and provided robust support for learning and development.

Limitations

However, RISC-V is not without its challenges:

- Being an open-standard, its ecosystem is still maturing, and compared to established architectures such as ARM or x86, RISC-V has fewer commercially-tested implementations. This can lead to concerns regarding toolchain maturity, proprietary support, and guaranteed performance under industrial standards.

- The very openness that is a strength of RISC-V can also introduce fragmentation. As companies develop custom extensions, there is a risk of diverging from the standard, which may hinder interoperability.

- The need to support both legacy software and emerging applications means that the community continuously grapples with balancing simplicity and functionality. This sometimes results in debates over which extensions to standardize and how to incorporate increasingly complex computing demands without compromising the core RISC-V philosophy.

Use Cases

Once primarily used in academic settings, RISC-V has transitioned into commercial products, demonstrating its versatility and industry-wide appeal.

- Embedded systems: RISC-V-based small-scale processors are widely used in IoT devices, sensors, and smart appliances. Their low power consumption and customizable nature make them ideal for resource-constrained applications.

- Automotive industry: Companies are integrating RISC-V cores into automotive applications where reliability and efficiency are essential.

- Data centers and high-performance computing (HPC): RISC-V is gaining traction in experimental and production deployments, offering scalable and power-efficient server designs.

- Specialized processing: RISC-V’s modular design enables the development of specialized cores for tasks such as machine learning, graphics acceleration, and secure processing. Many companies are incorporating RISC-V cores into heterogeneous system-on-chip (SoC) architectures that combine custom hardware accelerators with a general-purpose controller, providing a balance between performance and extensibility.

- Digital communication: This sector is exploring RISC-V implementations for wireless and networking applications, including 5G modems and baseband processors. The customizable architecture allows designers to fine-tune performance for specific communication protocols.

Challenges and Best Practices

Developing and deploying RISC-V solutions, while offering significant benefits, comes with its own set of challenges.

One of the common issues is the relative immaturity of the ecosystem. While the community is growing rapidly, integrating diverse toolchains, simulators, and verification frameworks requires careful coordination. This is particularly true when designing complex systems that may include custom extensions beyond the standard set.

A best practice adopted by many designers is to closely follow the RISC-V specifications and guidelines published by RISC-V International. Adhering to these standards helps prevent fragmentation and ensures that designs remain compatible with broader ecosystem tools and software.

Verification and testing practices are another area that come with challenges. Given the modular design of RISC-V, verifying that all interactions between base ISA functions and optional extensions work as intended is critical. Best practices include rigorous simulation, formal verification of critical modules, and iterative testing of hardware-software integration. The use of open-source simulators and reference designs can significantly speed up the verification process and reduce the risk of latent bugs.

Custom extensions should be approached with careful documentation and adherence to interoperability guidelines. Maintaining a balance between innovation and standard compliance helps ensure that the benefits of RISC-V’s open architecture are realized without compromising system integrity. Verification teams are encouraged to employ systematic testing frameworks, such as regression testing and verification IP (VIP) suites, to validate their designs across various configurations.

RISC-V vs. ARM vs. x86: Which One Is Better?

RISC-V is rapidly gaining momentum as more startups and established companies alike embrace it over long-standing proprietary architectures. It’s not a matter of which ISAis better, but what suits each specific use case. Each architecture has its strengths, making all three suitable for different industry needs. Below is a comparison based on key factors:

| Feature | RISC-V | ARM | x86 (Intel/AMD) |

|---|---|---|---|

| Instruction Set | RISC, customizable | RISC, fixed license | Complex instruction is computing (CISC), backward compatibility |

| Licensing | Free, open-source | Licensed from ARM Holdings | Proprietary, controlled by Intel and AMD |

| Customization | Highly customizable (ISA can be modified) | Limited customization (license-dependent) | No customization, fixed ISA |

| Performance | Optimized for efficiency, scalable | Power-efficient, optimized for mobile/embedded | High performance but power-hungry |

| Power Efficiency | High (depends on implementation) | Very high (designed for mobile and embedded) | Lower than RISC architectures |

| Ecosystem | Growing, supported by many startups and academia | Well-established in mobile and embedded markets | Mature ecosystem, dominant in desktops and servers |

| Use Cases | IoT, embedded, custom hardware, HPC, AI | Mobile, embedded systems, low-power computing | PCs, servers, gaming, high-performance workloads |

| Security | Open-source transparency, customizable security features | Strong security features via proprietary implementations | Extensive security but more complex due to legacy support |

| Software Support | Emerging but improving, requires adaptation | Wide software support (mobile, embedded, cloud) | Extensive support with backward compatibility |

Future Outlook

The future of RISC-V looks particularly promising as the semiconductor industry continues to explore open, flexible, and cost-effective alternatives to traditional proprietary architectures. The continued growth of the RISC-V community, coupled with active participation from both academia and industry giants, is accelerating the maturity of the ecosystem.

Research and development are focusing on addressing current challenges related to toolchain robustness, integration of advanced microarchitectural features, and ensuring security through standardized extensions. As designs become more sophisticated, efforts aimed at harmonizing custom extensions with the core ISA remain critical. The roadmap for RISC-V includes enhanced support for high-performance computing features such as simultaneous multi-threading (SMT), improved virtualization capabilities, and advanced power management techniques.

There is also significant momentum in developing certified cores for safety-critical and mission-critical applications such as automotive and aerospace, where reliability and conformity to standards are paramount. The ever-growing interest from startups and established companies alike suggests that RISC-V will increasingly permeate diverse market segments ranging from consumer electronics to industrial controllers.

Furthermore, the collaborative nature of RISC-V International means that consensus-driven decisions about future extensions and enhancements are more likely to yield balanced designs that cater to a wide range of application needs. This progressive evolution bodes well for long-term adoption and signals a shift in how processor architectures are developed and licensed.

Overall, the trajectory of RISC-V points towards an era in which open hardware standards redefine the competitive landscape, stimulating innovation, reducing development costs, and democratizing access to cutting-edge processor technology worldwide.

How AMIQ EDA’s Tools Help with RISC-V

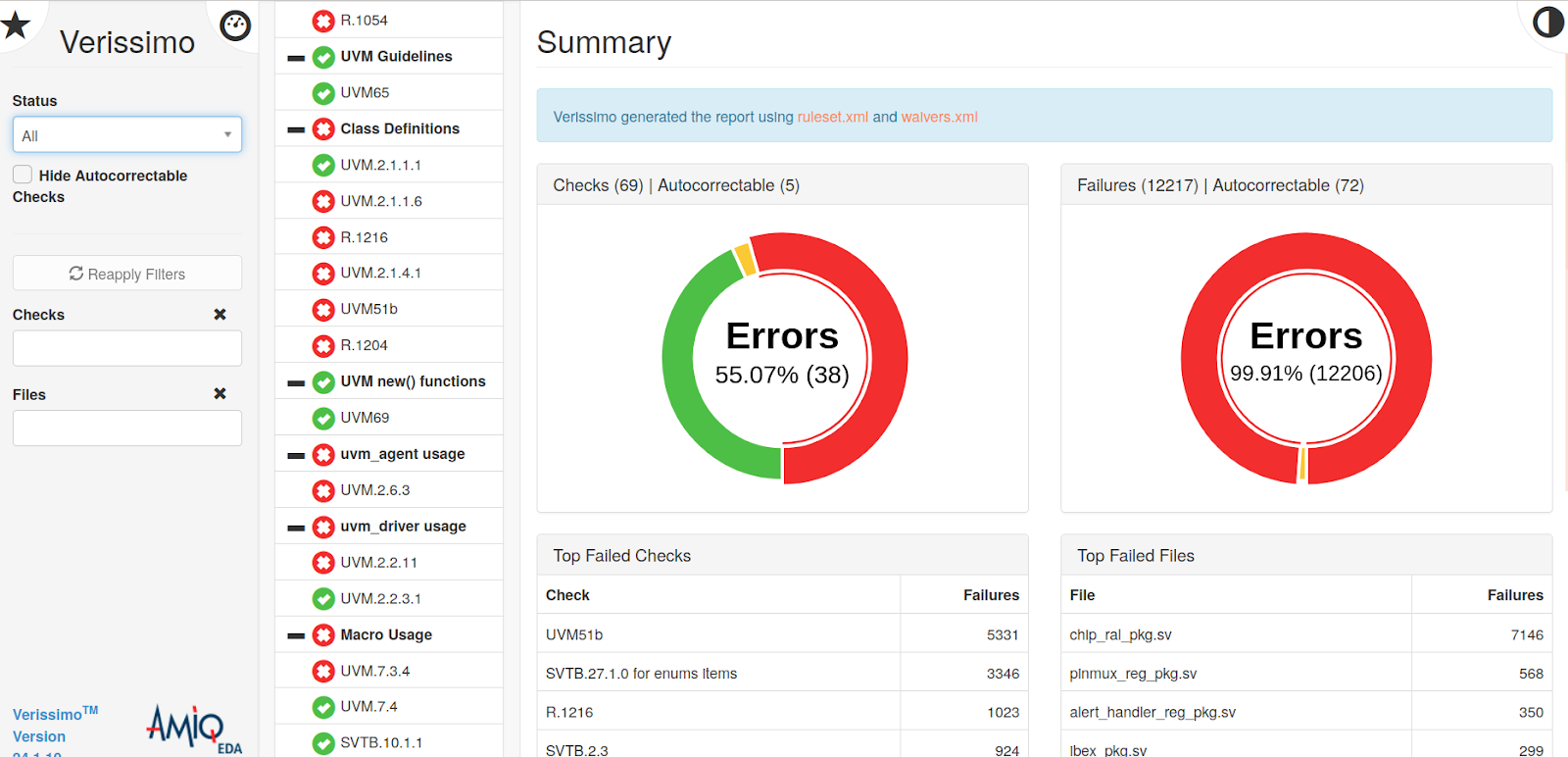

For teams developing RISC-V based cores and verification environments, maintaining a high level of code quality and ensuring simulator portability are key challenges. AMIQ EDA’s Design and Verification Tools (DVT) products, including DVT IDE for Eclipse and Visual Studio (VS) Code and Verissimo SystemVerilog Linter, are designed to integrate seamlessly into continuous integration (CI) flows. This integration enables automated lint checks on every code commit, ensuring that even subtle coding issues are identified early in the development process.

Verissimo SystemVerilog Linter goes beyond syntax and semantic checks by flagging potential issues that may not be consistently supported across different simulators. For example, in environments where custom RISC-V extensions and UVM-based testbenches are being developed, the linter can detect non-standard constructs and deviations from the established coding guidelines. This proactive analysis helps ensure that RISC-V implementations and verification environments remain vendor-neutral and maintain a high level of code readability and quality.

Additionally, the flexibility of these tools allows for highly customizable linting rules, which teams can refine to match the specific requirements of their RISC-V projects. Collaborations with groups such as OpenHW Foundation have shown that integrating these tools into a CI flow not only uncovers code quality issues—such as problematic overrides or usage of unsupported constructs—but also provides an openly accessible dashboard of linting results. This transparency fosters a collaborative approach to maintaining coding standards within an open-source ecosystem. A tuned Verissimo lint rule set is available to all OpenHW users and continuously executed every few hours on AMIQ’s servers.

Overall, by embedding automated lint checks early in your development cycle with AMIQ EDA’s tools, designers and verification engineers reduce the risk of latent bugs and improve simulation efficiency. This focus on continuous integration and rigorous code quality not only streamlines development but also supports the design of robust, portable, and maintainable RISC-V cores and verification environments.