What Is DVT IDE

Design and Verification Tools (DVT) IDE is an integrated development environment for Verilog, SystemVerilog, Verilog AMS, VHDL, UPF, CPF, e Language, and PSS, helping design and verification engineers significantly improve their productivity.

Unlike plain text editors providing regular-expression-based capabilities, DVT IDE compiles the code and signals errors as you type, speeds up code writing using auto-complete and quick-fix proposals, and allows you to find anything you are looking for instantly.

DVT IDE can give you in seconds what would likely have taken you several minutes or hours to find and do by hand.

It is similar to well-known programming tools like Visual Studio®, NetBeans®, and IntelliJ® that are commonly used in the software world

Ensures higher quality development.

Simplifies debugging and legacy code maintenance.

Allows easy navigation through complex code.

Accelerates language and methodology learning.

Increases productivity and reduces time to market.

Speeds up code writing.

DVT IDE helps you overcome the limitations of plain text code editors and address today’s project complexity more efficiently. It enables faster and smarter code development and simplifies legacy code maintenance for novices and experts alike who work with common HDLs and HVLs.

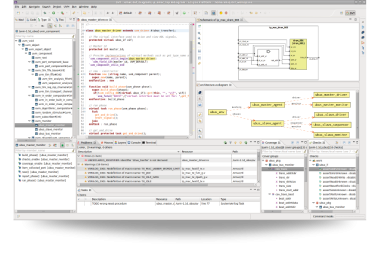

It consists of a compiler, a smart multi-language code editor, an intuitive GUI, an AI assistant, and a comprehensive set of features that help with code inspection, navigation, and debugging. In addition, DVT IDE includes several capabilities that are specific to the hardware design and verification domains, such as class and structural browsing, signal tracing, and verification methodology support.

DVT IDE works as an Eclipse Platform plug-in or as a Visual Studio Code extension. Both Eclipse and VS Code are used by tens of thousands of engineers worldwide. DVT IDE inherits the best features and practices of the platforms and integrates within a large ecosystem of 3rd party extensions.

Multi-Language Support

DVT IDE provides built-in support for the most widely used hardware design and verification languages used in modern ASIC and FPGA development.

- Verilog

- SystemVerilog

- Verilog AMS

- VHDL

- UPF

- CPF

- e Language

- PSS

Key Features

Real-Time Code Editing and Compilation

- On-the-fly standard compliant compilation. DVT IDE uses an IEEE standard compliant compiler (IEEE 1800 SystemVerilog, IEEE 1647 e Language, IEEE 1076 VHDL, and IEEE 1801 Low Power). There is no need to invoke the simulator or synthesis tool to make sure your code compiles without errors. DVT IDE performs on-the-fly incremental compilation and highlights the errors in real time, as you type.

- Advanced code editing capabilities such as autocomplete, quick fixes, macro expansion, intelligent code formatting, refactoring, connecting module instances, code templates, and in-line reminders for task tracking - everything you expect from a top editor for industry-standard languages.

- AI-assisted development that helps create and improve HDL code directly in DVT IDE, using project-aware context to improve accuracy.

Advanced Code Navigation and Design Exploration

- Code and project navigation features such as hyperlinks, semantic search, class and structural browsing (e.g. class hierarchy, design hierarchy), check and coverage views, dynamically created UML diagrams and design diagrams, and trace port connections. With these features DVT IDE enables you to navigate easily through tens of thousands of code lines, locate the relevant information, inspect a class or module structure, and understand the source code quickly.

Built-In Verification Methodology Support

- Verification methodology support. DVT IDE supports the Universal Verification Methodology (UVM), Open Verification Methodology (OVM) , and Verification Methodology Manual (VMM). It includes a UVM/OVM automated compliance-checking capability and a built-in OVM-to-UVM Migration Wizard that offers advanced transition capabilities using refactoring scripts.

Seamless Toolchain and Workflow Integration

- Integration with the NCSim, Specman, VCS, and Questa simulators for simplified simulation analysis and debugging. You can easily invoke a simulator and then visualize and browse its output on the DVT IDE console through a smart log viewer. The log simulation errors and warnings are hyperlinked to the problematic source code.

- Integration with revision control systems like Git, Subversion, and ClearCase as well as bug tracking systems.

Mixed-Language Development and Customizable Workspace

- Cross-language capabilities for mixed-language projects allow you to work with source code written in multiple languages, navigate seamlessly through large projects, easily see the big picture, and understand the whole design.

- Customizable views. Besides the source code window opened into the GUI, at any given moment you can bring in and move around the necessary information, look from a higher perspective, or drill down into details. For example, a GUI perspective can include views of the source code, types, class hierarchy, layers, errors and warnings, tasks, macros, and diagrams.

Why choose DVT IDE

- Quickly fix the errors flagged as you type (incremental compilation).

- Move around in your source code using hyperlinks.

- Speed up code writing and avoid typos using auto-complete.

- Continuously improve your code using refactoring.

- Easily create and reuse code and project templates.

- Understand the project using high-level structural views like class or design hierarchies.

- Trace a signal throughout your design.

- Visualize the project architecture using UML Diagrams or Design Diagrams.

- Place reminders and track tasks.

- Integrate projects developed using mixed languages, such as VHDL, Verilog, or SystemVerilog in combination with C/C++.

Frequently Asked Questions

Is DVT IDE a Verilog IDE?

Yes. DVT IDE provides full support for Verilog development, including real-time compilation, advanced code editing, semantic navigation, and project-wide analysis. Engineers can write, explore, and understand Verilog code efficiently using features such as autocomplete, structural browsing, and cross-file navigation.

Is DVT IDE a VHDL IDE?

Yes. DVT IDE supports VHDL development through its built-in IEEE 1076–compliant compiler, which understands the language syntax and design structure defined by the standard. This allows the IDE to interpret VHDL code correctly within complex projects and provide accurate feedback directly in the development environment.

Does DVT IDE support SystemVerilog?

Yes. DVT IDE supports SystemVerilog and is designed to handle large verification environments, including complex class-based code and testbench structures. It makes it easier to understand the relationships between components and provides visibility across the entire verification environment.

Does DVT IDE support SystemVerilog UVM?

Yes. DVT IDE supports SystemVerilog UVM, including features for navigating class hierarchies, analyzing verification components and TLM port connections, and working with UVM-based environments. It also includes tools to support migration from OVM to UVM.

Can I use DVT IDE as a Verilog editor in VS Code?

Yes. DVT IDE is available as an extension for Visual Studio Code, allowing engineers to work with Verilog directly within the VS Code environment while benefiting from DVT’s language-aware capabilities.

Learn how to get started with DVT from our tutorial on how to use DVT IDE in Visual Studio Code.

Does DVT IDE support Eclipse for Verilog development?

Yes. DVT IDE is available for Eclipse, providing advanced capabilities for Verilog and other common HDLs and HVLs.

Check out our tutorial and see how easy it is to start your first DVT IDE Eclipse project.

Is DVT IDE available as a VHDL editor for Windows?

Yes. DVT IDE can be used on Windows and supports development in VHDL.

Learn more from our tutorial on how to start DVT IDE on Windows OS.

How is DVT IDE different from a plain text Verilog editor?

Unlike a plain text editor, DVT IDE performs source code analysis and compilation of HDL/HVL projects to enable advanced development features such as error detection, hyperlinks, code navigation, code refactoring, and autocomplete. This helps engineers work more efficiently with large Verilog, SystemVerilog, and VHDL codebases.

Can DVT IDE be integrated with other tools?

Yes. DVT IDE can be used together with specialized tools that support different stages of the hardware design and verification workflow.

For example, teams can use:

- DVT Debugger to analyze simulation results and debug complex verification environments

- Verissimo SystemVerilog Linter to perform static code analysis and enforce coding guidelines

- Specador Documentation Generator to automatically generate documentation from HDL/HVL code

- DVT MCP Server for advanced automation and AI-assisted workflows to enable integration with modern development environments and tools