What Is DVT MCP Server

DVT MCP Server is a tools server that supports Verilog, SystemVerilog, VHDL, and the e language, enabling AI agents and LLM-based code generators to understand, modify, and debug real-world design and verification projects efficiently and accurately.

Why You Need More Than an LLM for Verilog, SystemVerilog, and VHDL

Design and verification languages pose unique challenges for AI agents. While these agents excel at programming with general-purpose languages, they often struggle with domain-specific languages due to limited training data.

These challenges are structural. HDLs and HVLs rely on concurrency, elaboration, and complex cross-file hierarchies that make reliable AI-assisted code generation difficult.

Providing agents with full project context is essential for producing valid results in design and verification projects, as it grounds their reasoning in accurate language semantics and facilitates early error detection.

Boosts accurate code generation.

Improves AI agent grounding.

Enhances large-project handling.

Speeds up AI agents.

Lowers token usage.

Enables agent fleets.

Enhances user experience.

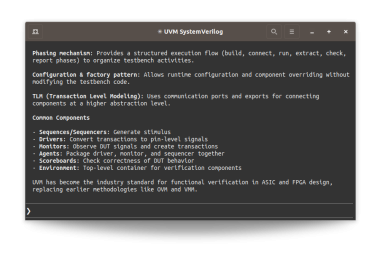

How It Works With AI Tools

DVT MCP Server provides AI agents access to essential tools for real-world design and verification projects. By closing the feedback loop on code generation through on-the-fly compilation and precise error reporting, it enables reliable AI-assisted iterative generation, validation, and correction of code.

By leveraging the elaborated design and verification full compilation hierarchy, it helps agents navigate complex projects, understand architectural intent, and accurately locate and reason about code constructs across the codebase.

Avoiding grep-based searches and reducing context overload, the server allows assistants to focus on relevant information. Precise, context-aware information delivered by AMIQ EDA tools can speed up debugging and improve correctness and accuracy.

DVT MCP Server is flexible and integrates seamlessly into existing workflows. It can run directly within DVT IDE to provide live project context to interactive AI assistants, or operate in batch mode to support fleets of agents, enabling scalable, parallel execution for large codebases and automated workflows, including refactoring, code migration, and automated debugging tasks.

Key Features

- Incremental compilation for AI-generated code.

- Architectural exploration API/tools (design hierarchy, verification hierarchy, compiled files).

- Semantic exploration API/tools (definitions, usages).

- Support for IDE AI agents including DVT AI Assistant (in DVT IDE), Cursor, GitHub Copilot, Cline, Claude Code, Codex.

- Support for batch mode AI agents and AI-based automation.

- Cross-language capabilities for mixed-language projects.

- Fully compliant with the Model Context Protocol (MCP) standard.

Why choose DVT MCP Server

- Validate AI-generated code.

- Avoid hallucinations and incorrect context grounding.

- Avoid grep-based searches to reduce context overload and token usage.

- Create more efficient and convergent AI workflows.

- Enable automated AI workflows through fleets of agents.

- Built by EDA Experts.

Security, Privacy and Data Handling

DVT MCP Server runs locally within the user’s controlled environment, keeping source code on internal infrastructure and operating under existing security policies, without external services, additional permissions, or outbound data transfer.

Frequently Asked Questions

Is DVT MCP Server a Verilog, SystemVerilog, or VHDL AI code generator?

No. DVT MCP Server is not a code generator. It works alongside AI tools and LLMs used for Verilog, SystemVerilog, and VHDL. It connects these tools to the actual project, where they validate and refine code using real compilation feedback.

What is a Verilog or VHDL MCP server, and how is DVT MCP Server different?

A Verilog or VHDL MCP server provides AI tools with structured access to design and verification data through the Model Context Protocol (MCP). DVT MCP Server uses compiled design data to expose this information, giving AI assistants access to the full project context rather than isolated code snippets.

Does DVT MCP Server support SystemVerilog and mixed-language projects?

Yes. DVT MCP Server supports Verilog, SystemVerilog, VHDL, and the e language, including mixed-language projects. It relies on the compiled design structure to help the AI model navigate and reason across languages and files.

Does DVT MCP Server depend on a specific LLM or AI model?

DVT MCP Server is model-agnostic. It works with any LLM or AI assistant that supports the Model Context Protocol (MCP). This means teams are not tied to a specific model or provider and can choose the tools that best fit their workflows.

Can DVT MCP Server be used with GitHub Copilot, Codex, or other AI assistants?

Yes. DVT MCP Server works with MCP-compatible AI assistants, including GitHub Copilot, Codex, and others, both in IDE environments and from the command line. It exposes compiler-backed project data through standard interfaces, giving these tools access to live design context to analyze code and validate changes within existing workflows, without losing project context.

Does DVT MCP Server support large and complex HDL projects?

Yes. DVT MCP Server is designed to work with large and complex design and verification codebases. It uses the full project hierarchy so AI assistants can navigate, analyze, and reason about code across modules and files, supporting accurate understanding at scale, even in multi-file, mixed-language environments.

Does DVT MCP Server run inside user infrastructure (on-premises)?

Yes. DVT MCP Server runs on-premises and fits within existing security and compliance requirements. Teams retain full control over their design data without introducing external dependencies or data transfer.

Can DVT MCP Server be used with other hardware design and verification tools?

Yes. DVT MCP Server works alongside existing design and verification tools and fits into current workflows. It works with AI assistants as well as other tools used for development, debugging, analysis, and documentation.

For example, teams can combine it with:

- DVT IDE for editing, navigating, and analyzing HDL code

- DVT Debugger for debugging simulation behavior and investigating issues

- Verissimo SystemVerilog Linter for static code analysis and coding guideline enforcement

- Specador Documentation Generator for generating documentation from HDL/HVL source code