Low Power Format Support

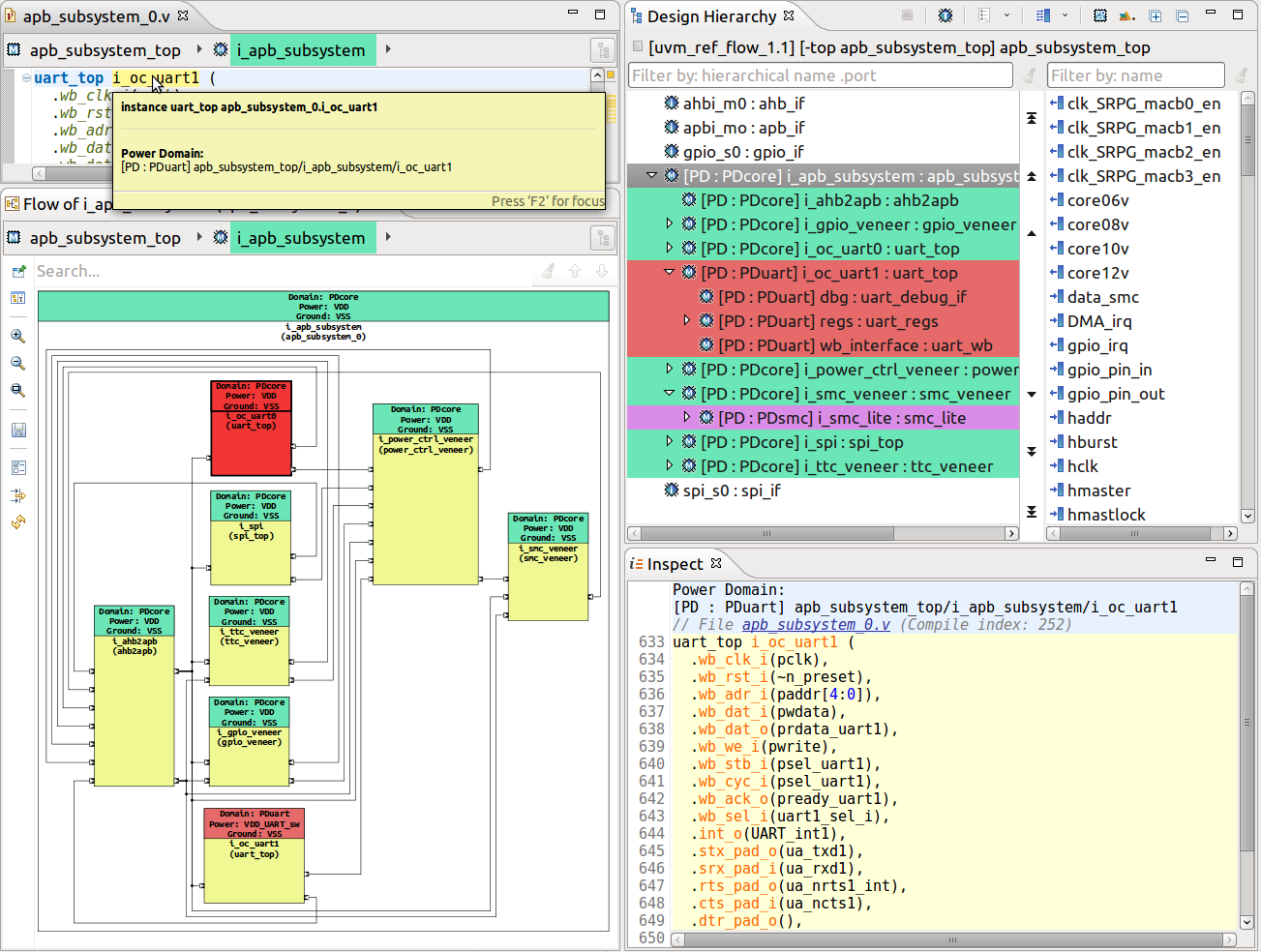

DVT analyzes power format files (either UPF or CPF) and presents power domain information in:

Design Hierarchy View - using labels and/or colors

Schematic Diagrams, Flow Diagrams and Block Diagrams - using labels and/or colors

Breadcrumb Navigation Bar - using colors and tooltips

Tooltips in the Verilog and VHDL Editors

Power format project nature

In order to work with power format files, you have to enable the Power Format nature for your project.

In the New DVT Project Wizard check UPF/CPF

For an existing project, right-click on it in the Project Explorer View, choose Change DVT Nature then check UPF/CPF

The Power Format nature works only in conjunction with at least one of Verilog or VHDL natures.

Power format files

Use one of the following build configuration directives to specify a power format file to be analyzed:

Compatibility mode |

Directive |

|---|---|

ANY |

+dvt_upf+<upf_file> +dvt_cpf+<cpf_file> |

ius.irun |

-lps_1801 <upf_file> -lps_cpf <cpf_file> |

vcs.vloganvcs.vhdlgan |

-upf <upf_file> |

questa.vlogquesta.vcom |

-pa_upf <upf_file> |

Power format analysis

At full build, after elaborating the design, DVT analyzes (interprets) the provided power format file and elaborates the power domains. TCL and power domain errors are detected and reported during this phase.

All analyzed power format files are decorated with a blue bullet. Files outside the project directory are automatically linked under the DVT Auto-Linked folder.

Note

By default, the working directory of the TCL interpreter is the DVT project directory. To change it, use +dvt_compilation_root within the invocation where the power format file is specified, for example:

+dvt_init

+dvt_compilation_root+/path/to/new/compilation/root

+dvt_upf /path/to/file.upf

Note

Environment variables defined using +dvt_setenv within the invocation where the power format file is specified are available in the TCL $::env array.

Tip

To print power format analysis debug information in the DVT Build Console add this directive to your build configuration file:

+dvt_pf_debug

Tip

If a file called dvt_pre_interpret.tcl exists in any of the the User and Common Settings Location it will be interpreted before the provided power format file. If several such files exist, they will all be interpreted, in precedence order of the User and Common Settings Locations. This mechanism allows you to define TCL variables or functions for debugging or deployment purposes.

Incremental power format analysis

Whenever you change a power format file which was analyzed during the full build phase, DVT triggers a power format file analysis and a power domain elaboration.

Whenever you change a design file (Verilog or VHDL) which was compiled during the full build phase, DVT triggers a power domain elaboration (analysis of power format files is not performed).

The following Common Power Format (CPF) and Unified Power Format (UPF) commands are supported by DVT:

CPF up to Version 2.1

create_power_domain -name <power_domain_name> -default -instances <instance_list> -exclude_instances <instance_list>set_hierarchy_separator <separator_character>set_instance <instance>include <cpf_file>

UPF (IEEE Std 1801™) up to Version 3.0

create_power_domain <power_domain_name> -elements <instance_list> -exclude_elements <instance_list> -include_scope -scope <scope>upf_version <version>set_scope <scope>load_upf <upf_file> -scope <scope> -version <version>