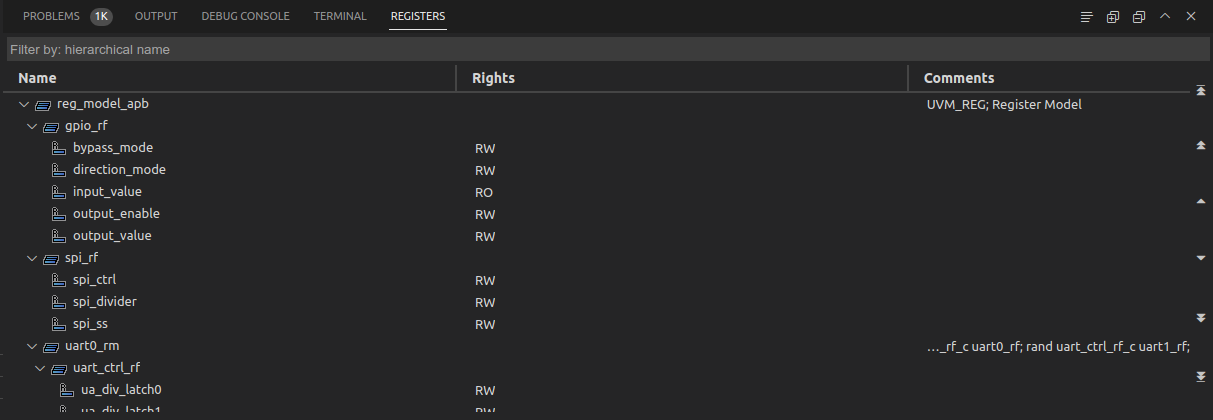

Registers View

The Registers View shows all the UVM registers within the register model hierarchy.

Open the Command Palette and run the View: Focus on Registers View command.

By default the view content is presented as a tree rooted in the register model and comprising of register blocks, register files, and individual registers as leaves.

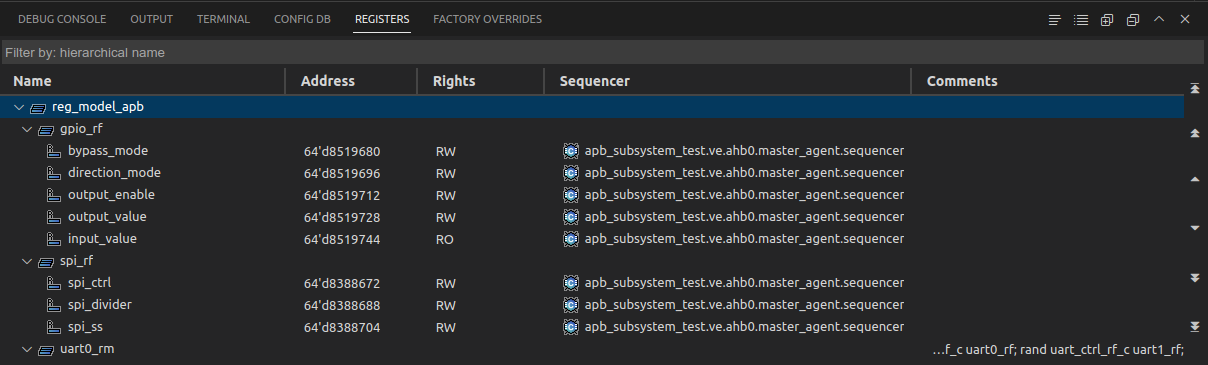

For each register, the view presents its name, access rights and source code comment. If setting a runtime elaborated Verification top, the view also shows the address and associated sequencer for each register.

Right-click on any register from the view and choose Show Diagram to visualize its bitfield diagram.

Tip

Double click to go to the register’s create call.

Tip

Use the Display Registers as List in Registers View button ( ) from the view header to switch to a flat list view, where the name represents a hierarchical path from the reg model to the reg. To switch back to the tree view, use the

) from the view header to switch to a flat list view, where the name represents a hierarchical path from the reg model to the reg. To switch back to the tree view, use the  button.

button.

Tip

If setting a runtime elaborated Verification top, you can change the Address Radix to be Decimal or Hexadecimal by modifying the DVT.registers.addressRadix preference.

Tip

If setting a runtime elaborated Verification top, by default the view is sorted alphabetically. Use the button  from the view header to Sort by address.

from the view header to Sort by address.