Extract to Variable

An expression inside a function or task can be extracted to a local variable.

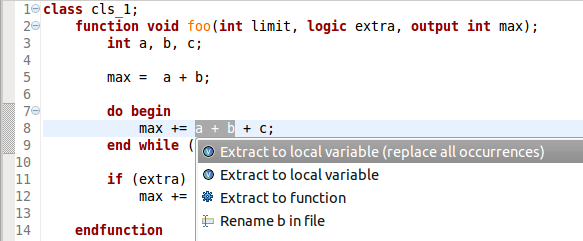

Select the expression and press Ctrl+1, select Extract to local variable from the list of quick assist proposals and press Enter.

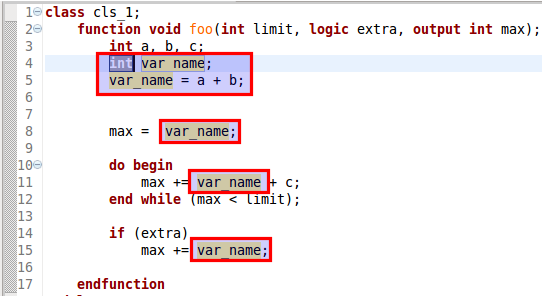

The variable is declared and initialized with the extracted expression in the correct scope.

Note

By default, if and loop conditions are evaluated to the logic data type, according to the IEEE 1800-2023 Standard for SystemVerilog. You can enforce the data type to bit by going to and enabling Enforce condition data type to bit.

This preference applies only when you select the whole condition.

Tip

You may change the variable name and type. Press tab to switch between the edit boxes.

Tip

If the expression occurs multiple times throughout the function, you may chose to replace all the occurrences with the newly created variable, or only the selected one.

Tip

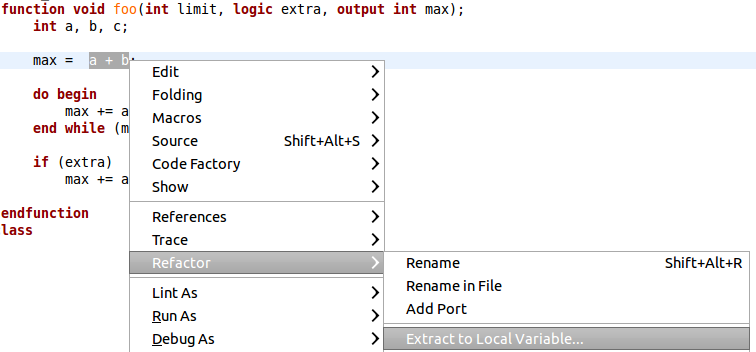

You can also Right-Click in the editor and go to Refactor > Extract….