UVM Browser

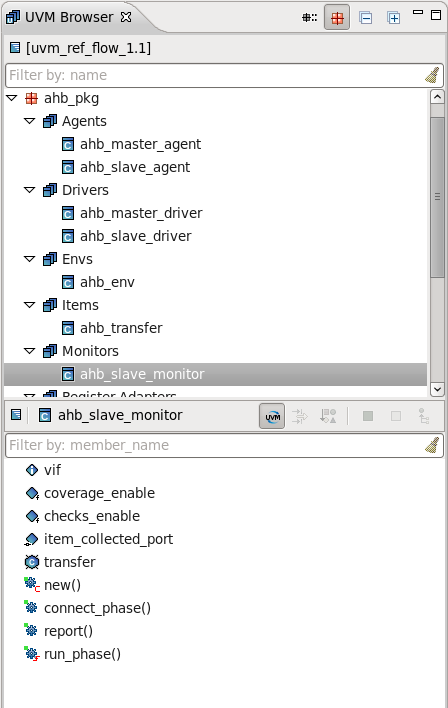

The UVM Browser View is an intuitive entry point for exploring all the classes of a UVM-based verification environment.

It allows you to explore UVM-based classes grouped by categories, like agents, monitors, drivers or sequences and easily inspect the UVM flow specific API, like overridden phases, class members registered to the factory or TLM ports.

Open the view from menu .

You can use CamelCase or Simple Regex to locate a specific element.

Toolbar |

||

|---|---|---|

|

Prepend Package Name |

Prepend the enclosing package name to the name of each class, useful when you explore for example all agents across packages. |

|

Group By Package |

Group classes by package. You may chose to see for example all agents across packages or to explore all categories in a specific package. |

The top UVM Types Panel presents all the UVM-based classes defined in your verification environment. For convenience they are grouped by categories like agents or monitors.

The inheritance hierarchy between classes is shown up to the UVM base class.

Description |

|

|---|---|

|

Class is declared under a different package than the parent package presented in the view’s tree because one of its children are declared under that parent package and “Group by Package” is enabled. |

|

Physical sequencer or sequence. A physical sequencer is a sequencer that is connected to a driver. A physical sequence always extends uvm_sequence parameterized with a class that extends uvm_sequence_item and contains `uvm_declare_p_sequencer macro with a physical sequencer as argument. |

The categories and their corresponding base classes are the following

Categories |

Base class |

Notes |

|---|---|---|

Agents |

uvm_agent |

|

Drivers |

uvm_driver |

|

Envs |

uvm_env |

|

Items |

uvm_sequence_item |

|

Monitors |

uvm_monitor |

|

Memories |

uvm_mem |

|

Other Components |

uvm_component |

Any class deriving from uvm_component which does not fall into any other category within this table. |

Other Objects |

uvm_object |

|

Ports |

uvm_port_base, uvm_tlm_if_base, uvm_tlm_extension_base, uvm_sqr_if_base, uvm_tlm_req_rsp_channel, uvm_tlm_fifo_base |

|

Registers |

uvm_reg |

|

Backdoor Registers |

uvm_reg_backdoor |

|

Frontdoor Registers |

uvm_reg_frontdoor |

|

Register Adapters |

uvm_reg_adapter |

|

Register Blocks |

uvm_reg_block |

|

Register Fields |

uvm_reg_field |

|

Register Sequences |

uvm_reg_sequence |

|

FIFO Registers |

uvm_reg_fifo |

|

Register Files |

uvm_reg_file |

|

Register Maps |

uvm_reg_map |

|

Register Predictors |

uvm_reg_predictor |

|

Scoreboards |

uvm_scoreboard |

|

Sequencers |

uvm_sequencer |

|

Sequences |

uvm_sequence |

|

Tests |

uvm_test |

The bottom Members Panel panel displays class members. You can toggle the UVM Members Mode on/off using the  button.

button.

In UVM Members Mode it displays the following members:

Virtual interfaces

Class members registered to the factory using the `uvm_field… macros

Class members of an UVM-based type (TLM ports included)

Overridden functions and tasks from parent UVM base classes

When the UVM Members Mode is off, the Members Panel behaves exactly like the Members Panel of the Type Hierarchy View.